- Ameya360 Component Supply Platform >

- Trade news >

- 2020年1-5月集成电路进口2011.5亿个,增加27.3%

2020年1-5月集成电路进口2011.5亿个,增加27.3%

据海关统计,今年1-5月,我国货物贸易进出口总值11.54万亿元人民币,比去年同期下降4.9%,降幅和前4个月持平。其中,出口6.2万亿元,下降4.7%;进口5.34万亿元,下降5.2%;贸易顺差8598.1亿元,减少1.2%。按美元计价,前5个月,我国进出口总值1.65万亿美元,下降8%。其中,出口8849.9亿美元,下降7.7%;进口7636.3亿美元,下降8.2%;贸易顺差1213.6亿美元,减少4.5%。

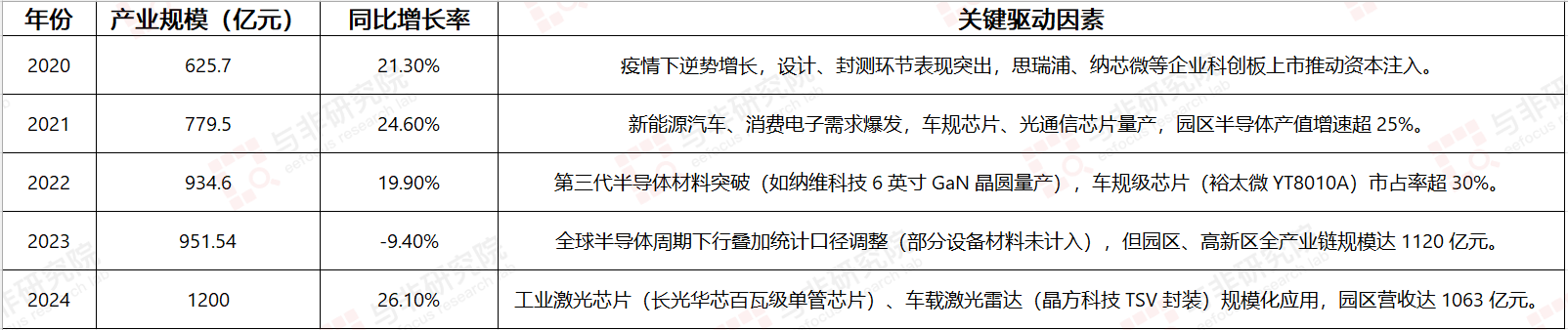

前5个月我国集成电路进出口数据

尽管近年来中国政府对集成电路行业花费多番心血,从扶持政策、支持投资等方面入手积极推动中国集成电路产业的发展。但在国内半导体市场迅速发展的同时,集成电路进口额也在不断攀升。

据了解,2019年中国集成电路进口数量为4451.34亿个,同比增长6.6%,2018年中国集成电路进口数量为4175.67亿个,同比增长10.8%。在进口金额方面,2019年中国集成电路进口金额为3055.5亿美元,同比下降2.1%。

而到了2020年1-5月,中国集成电路进口数量达到2011.5亿个,同比增加27.3%,进口金额为8794.3亿元人民币,同比增长14.5%。据中商产业研究院数据库显示,2020年5月中国集成电路出口量为206.6亿个,同比增长23.5%,出口金额为90.14亿美元,同比增长18.7%。不仅是进口量,在出口量方面我国集成电路均由较好的增长。

虽然我国集成电路出口量有增加,但是与进口量和进口金额相比,我国集成电路仍面临着巨大的挑战:我国是世界第一大集成电路产品消耗国但在半导体方面我国对外依赖程度高、自给率低下。同时,中国半导体产业经过多年发展,还存在产业结构与需求之间失衡,核心集成电路的国产芯片占有率低的现象。

全球半导体行业景气度回升

虽然2020年上半年,中国经济乃至全球经济的表现并不尽人意,但是在集成电路进出口数据方面却有较好的成绩。这究竟是什么原因导致?

从2019年下半年开始,全球半导体行业的景气度开始回升。由于5G通信及AI智能发展的需求拉动,随着云计算、大数据、物联网等领域的逐步成熟,预计未来3年我国集成电路市场仍将保持稳定增长。同时,集成电路行业将呈现三大发展趋势:IC设计行业将往高端化方向发展;集成电路行业将向发展中国家进行迁移;封测产业国产化进程加快。

在此背景下,甚至有分析机构预测,我国集成电路行业市场规模将保持20.3%的增速,2020年集成电路市场规模达到9448亿元人民币,到2025年,有望达到23773亿元人民币。另外,还有一个值得关注的原因,近期美国频频针对华为等中资企业,并最终加大了禁售力度,不排除上半年有部分企业开启疯狂囤货模式。据报道,在过去一年里,华为一直都在为美国现在推出的这个事实性封杀做准备,目前已经囤足了2年份的高端芯片产品。

在出口方面,中国复工复产良好,对其他国家生产起到了一定的替代作用,这导致中国集成电路芯片的出口增加。

其他行业的数据进出口数据

机电产品和服装等出口下降,纺织品出口增长。前5个月,我国机电产品出口3.64万亿元,下降4%,占出口总值的58.7%。其中,自动数据处理设备及其零部件出口5086.1亿元,增长1.8%;手机2756.5亿元,下降5.6%。

同期,包括口罩在内的纺织品出口4066.6亿元,增长25.5%;服装2678.1亿元,下降20.3%;塑料制品1872.6亿元,增长2.1%;家具1226.7亿元,下降14%;鞋靴821.1亿元,下降28.5%;玩具567.4亿元,下降11.8%;箱包510.5亿元,下降27.6%。此外,钢材出口2500.2万吨,减少14%;汽车(含底盘)37.7万辆,减少16.9%。

铁矿砂、原油、天然气、大豆等商品进口量增加,大宗商品进口均价以下跌为主。前5个月,我国进口铁矿砂4.45亿吨,增加5.1%,进口均价为每吨629元,上涨6.7%;原油2.16亿吨,增加5.2%,进口均价为每吨2567.4元,下跌21.2%;煤1.49亿吨,增加16.8%,进口均价为每吨503.4元,下跌4.7%;天然气4012万吨,增加1.9%,进口均价为每吨2642.1元,下跌14.7%;大豆3388.3万吨,增加6.8%,进口均价为每吨2770.2元,下跌1.7%;初级形状的塑料1471.2万吨,减少1.3%,进口均价为每吨9039元,下跌10.3%;成品油1340.3万吨,减少9.3%,进口均价为每吨3037.2元,下跌18.3%;钢材546.4万吨,增加12%,进口均价为每吨7043.6元,下跌13.9%;未锻轧铜及铜材218.5万吨,增加12.4%,进口均价为每吨4.3万元,下跌6.3%。

此外,机电产品进口2.36万亿元,下降0.9%;其中集成电路2011.5亿个,增加27.3%,价值8794.3亿元,增长14.5%;汽车(含底盘)27.8万辆,减少36.9%,价值928.8亿元,下降31.3%。

与贸易伙伴的进出口数额

对东盟进出口增长,对欧盟、美国和日本进出口下降前5个月,东盟为我第一大贸易伙伴,我与东盟贸易总值1.7万亿元,增长4.2%,占我外贸总值的14.7%。其中,我对东盟出口9366.2亿元,增长2.8%;自东盟进口7598.6亿元,增长6%;对东盟贸易顺差1767.6亿元,减少9%。

欧盟为我第二大贸易伙伴,与欧盟贸易总值为1.61万亿元,下降4.4%,占我外贸总值的13.9%。其中,我对欧盟出口9688.2亿元,下降1%;自欧盟进口6373.2亿元,下降9%;对欧盟贸易顺差3315亿元,增加19.1%。

美国为我第三大贸易伙伴,中美贸易总值为1.29万亿元,下降9.8%,占我国外贸总值的11.1%。其中,我国对美国出口9643.9亿元,下降11.4%;自美国进口3218.4亿元,下降4.5%;对美贸易顺差6425.5亿元,减少14.5%。日本为我国第四大贸易伙伴,中日贸易总值为8463.6亿元,下降0.3%,占我国外贸总值的7.3%。其中,对日本出口3961亿元,增长1.6%;自日本进口4502.6亿元,下降1.8%;对日贸易逆差541.4亿元,减少21.1%。

Previous:博通暗示苹果新iPhone将延后发布

Next:加拿大两大电信商宣布弃用华为!

Online messageinquiry

集成电路的概念及分类

“芯”为何物?一篇关于集成电路的详细解读

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| RB751G-40T2R | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments |

| model | brand | To snap up |

|---|---|---|

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BP3621 | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: