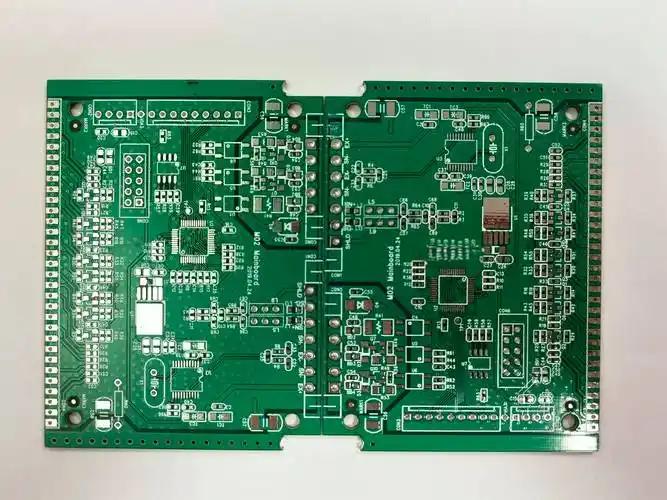

PCB元件焊接基本要点

PCB元件焊接要点,你了解几点?

焊接前:

1、工作台:必须整洁、干净、防静电,应采用防静电工/器具,戴好防静电手腕带。

2、工具:应有锡线座、元件盒、焊枪、焊台、镊子、剪钳等焊接工具和防护工具。

3、电路板:检查PCB板线路,有无短路、断路等。

4、物料:请确认好是正确的元件,元件有无极性要求,焊盘和元件脚有无氧化,若有则焊接前要要细砂纸打磨干净,涂上助焊剂。

焊接中:

1、安全、科学使用电烙铁,烙铁要接地,以防焊接时由于漏电而击穿元件,推荐使用白光可调电烙铁,有铅焊接时温度在350°C左右,无铅焊接时380°C左右。若烙铁头存在氧化层,需在高温海绵上擦拭干净。烙铁使用前要上锡:烙铁烧热到刚能融化焊锡时涂上助焊剂,再将焊锡均匀涂在烙铁头上。不使用时关闭烙铁电源。

2、元件焊接顺序:以先焊接好的元件不影响后面元件的焊接为原则,一般先焊接体积较小的电阻电容等元件,后焊接体积较大的元件,接插件最后焊接。

3、元件在板上的放置:应整齐、居中、贴板面放置,注意元件极性。

4、焊接操作姿势:烙铁到鼻子的距离在20~30cm为宜。

5、焊接时要求:应保证所有元件不移动位置。焊接头不可施加压力,先用焊锡接触焊点,再用烙铁头沿45°方向融化焊锡,待焊锡融化并浸没元件引脚后沿着引脚轻轻上提,焊接用时大约2~3秒。焊锡未完全凝固前不要晃动元件,以免造成虚焊。适当使用助焊剂。

6、焊接时间不可过长,也要尽量避免重复焊接,以免损坏元件。

焊接后:

1、检查有无漏焊、错焊(极性焊反)、短路、虚焊等现象。

2、检查焊点是否有适当的焊料,焊点应成圆锥形、整体饱满、光滑均匀、无针孔、有光泽,不应有毛刺、间隙及裂纹,焊点表面要清洁无松香渍。焊锡应包围引脚且不应过多。如果有引线,引脚,其露出引脚长度在1-2mm之间。

3、焊接后的废料应清理干净,及时丢到垃圾桶里。

4、焊接工具使用完要放回原位。

5、要正确使用洗板水清理PCB板上的残留物如锡渣、锡碎、元件脚等。应做好保护措施,因洗板水具有挥发性、可燃性。用剩的应装好、摆放好,不要浪费。

6、通电检测:先用万用表电阻档测量电源输入端有无短路现象,如有,应在加电前排除。再根据原理图对进行电路检查。

7、通电完成后必须按清单装配好IC,再调试。完成后用静电袋包装好PCB,不能随意摆放。

贴装元件焊接规范:

1、用镊子小心将贴片元件放到PCB板上,使其与焊盘对齐,并摆放在正中央,元件方向正确。

2、焊接前先在焊盘上涂助焊剂,并用烙铁处理一下以免镀锡不良或被氧化,元件无需处理。

3、焊接时要保持烙铁尖与被焊引脚并行,防止因焊锡过量发生搭接。

4、使用烙铁拖焊时,烙铁只能轻轻在引脚上滑过,否则就要碰弯贴片元件的引脚。

5、焊完所有的引脚后要检查焊点质量:焊点应光滑、饱满、发亮,不要虚焊、漏焊。

Previous:掌握高频电路:深入了解电路性能的关键指标

Next:全面掌握芯片散热设计基本概念

Online messageinquiry

PCB设计中降低电磁干扰的常用方法分享

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| RB751G-40T2R | ROHM Semiconductor | |

| CDZVT2R20B | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| TPS63050YFFR | Texas Instruments | |

| STM32F429IGT6 | STMicroelectronics | |

| BP3621 | ROHM Semiconductor | |

| ESR03EZPJ151 | ROHM Semiconductor |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: