- Ameya360 Component Supply Platform >

- Trade news >

- 半导体芯片中,什么是多晶硅耗尽效应?

半导体芯片中,什么是多晶硅耗尽效应?

1. 引言:多晶硅栅极的重要性及耗尽效应的问题

在现代集成电路制造领域,多晶硅栅极是场效应晶体管(FET)的核心组件,其性能直接决定着晶体管的开关特性与集成电路的整体功能。凭借良好的电学性能、与现有硅基工艺的高兼容性,多晶硅栅极长期以来成为集成电路制造的首选材料,在推动晶体管尺寸不断缩小、性能持续提升方面发挥了关键作用。

然而,随着集成电路制造工艺向纳米级不断迈进,多晶硅栅极耗尽效应逐渐成为制约器件性能提升的关键瓶颈。该效应不仅影响晶体管的开关速度与驱动能力,还会导致电路功耗增加、可靠性下降,严重阻碍了集成电路产业的进一步发展。

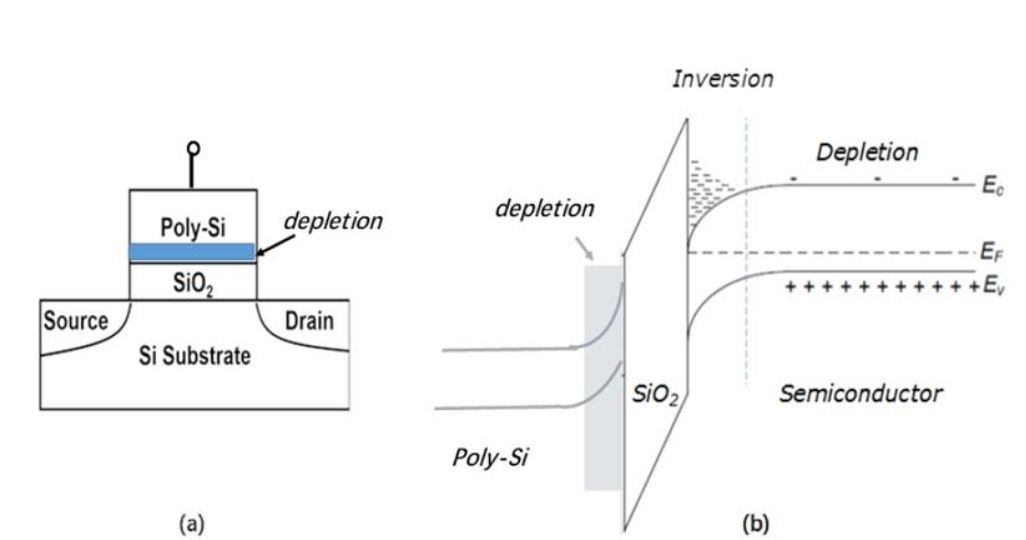

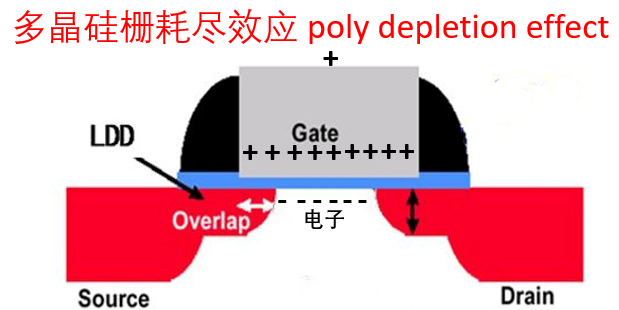

2. 耗尽效应的物理机制

多晶硅栅极耗尽效应的产生源于栅极与硅衬底间的电荷分布变化。当栅极施加电压时,会在电介质与沟道界面吸引少数载流子,形成反型载流子分布。为维持电中性,电介质与多晶硅界面附近会出现载流子积累,进而耗尽附近半导体的电荷。当半导体电荷完全耗尽时,该区域呈现绝缘特性,等效增大了栅介质的有效厚度。尽管耗尽层厚度极薄,仅相当于几个埃的二氧化硅厚度(NMOS 约 2 - 4 埃,PMOS 约 3 - 6 埃),但在栅介质厚度不断缩减的纳米级工艺中,其对器件性能的影响变得不容忽视。此外,栅介质厚度变薄时,相同栅极电压下内建电场增强,促使更多载流子积累,进一步加剧耗尽效应。

3. 耗尽效应对器件性能的影响

耗尽效应会显著降低器件的电学性能。由于耗尽层的存在,栅极对沟道的控制能力减弱,导致晶体管的阈值电压漂移、亚阈值摆幅增大,影响器件的开关速度与信号传输能力。同时,耗尽效应还会增加栅极电容,导致充放电时间延长,进一步降低电路的工作频率。此外,耗尽效应引起的电荷分布不均会使器件的漏电流增大,不仅增加了电路的静态功耗,还会产生额外的热量,影响集成电路的稳定性与可靠性。

4. 传统解决方法的局限(如掺杂浓度)

提高多晶硅栅极的掺杂浓度曾是缓解耗尽效应的常用方法。通过增加自由载流子浓度,可减少耗尽现象的发生。然而,随着工艺节点的不断缩小,如28纳米以下,这一方法逐渐面临诸多限制。一方面,栅极掺杂浓度已接近饱和状态,难以进一步提升;另一方面,高浓度掺杂会引发严重的工艺问题。以 PMOS 为例,高浓度的硼掺杂极易穿透栅介质,破坏器件结构,影响器件性能与可靠性。目前,NMOS 掺杂浓度需控制在 10²⁰ cm⁻³ 以下,PMOS 掺杂浓度需控制在 10¹⁹ cm⁻³ 以下,这使得通过提高掺杂浓度解决耗尽效应的途径愈发困难。

5. 金属栅极的引入及其优势

鉴于传统方法的局限性,金属栅极在 28nm 节点及以下工艺中逐步得到应用,如HKMG工艺28纳米以下先进制程为何离不开HKMG。金属具有极高的自由载流子浓度,从根本上避免了耗尽效应的产生。采用金属栅极后,晶体管的阈值电压稳定性显著提高,亚阈值摆幅减小,开关速度与驱动能力大幅提升。同时,金属栅极还能有效降低栅极电阻与电容,减少信号传输延迟,提高电路的工作频率。此外,金属栅极与高K电介质的结合使用,进一步优化了器件的电学性能,降低了功耗,为集成电路的持续发展提供了有力支撑。

6. 结论与未来展望

多晶硅栅极耗尽效应是集成电路纳米级工艺发展过程中面临的重要挑战,传统解决方法的局限性促使金属栅极成为主流解决方案。金属栅极的引入有效克服了耗尽效应的影响,推动了集成电路性能的大幅提升。然而,随着集成电路向更小尺寸、更高性能方向发展,新的挑战依然存在。未来,需要进一步探索新型栅极材料与工艺技术,优化器件结构设计,以满足不断增长的高性能、低功耗需求,持续推动集成电路产业的创新与发展。

Previous:兆易创新的模拟雄心:赋能国产替代一站式系统解决方案

Next:兆易创新:触感升级,打造得芯应手的体验

Online messageinquiry

- Week of hot material

- Material in short supply seckilling

| model | brand | Quote |

|---|---|---|

| CDZVT2R20B | ROHM Semiconductor | |

| MC33074DR2G | onsemi | |

| BD71847AMWV-E2 | ROHM Semiconductor | |

| TL431ACLPR | Texas Instruments | |

| RB751G-40T2R | ROHM Semiconductor |

| model | brand | To snap up |

|---|---|---|

| BP3621 | ROHM Semiconductor | |

| STM32F429IGT6 | STMicroelectronics | |

| ESR03EZPJ151 | ROHM Semiconductor | |

| BU33JA2MNVX-CTL | ROHM Semiconductor | |

| IPZ40N04S5L4R8ATMA1 | Infineon Technologies | |

| TPS63050YFFR | Texas Instruments |

Qr code of ameya360 official account

Identify TWO-DIMENSIONAL code, you can pay attention to

Please enter the verification code in the image below: